Low-Cost & Design-flexible 3D-IC **Packaging Solutions**

Vincent (Woopoung) Kim

**DSRA-AVP** SAMSUNG AVP (Advanced Packaging)

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

## Challenges of Today

SAMSUNG

### Cost

Moore's law slows down while costs continue to increase

### Performance

Power efficiency and bandwidth are limited by physical constraint

### Memory BW

Bottle-neck of system performance is memory bandwidth

• Our answer to today's challenges is 3D ICs and Advanced Packaging

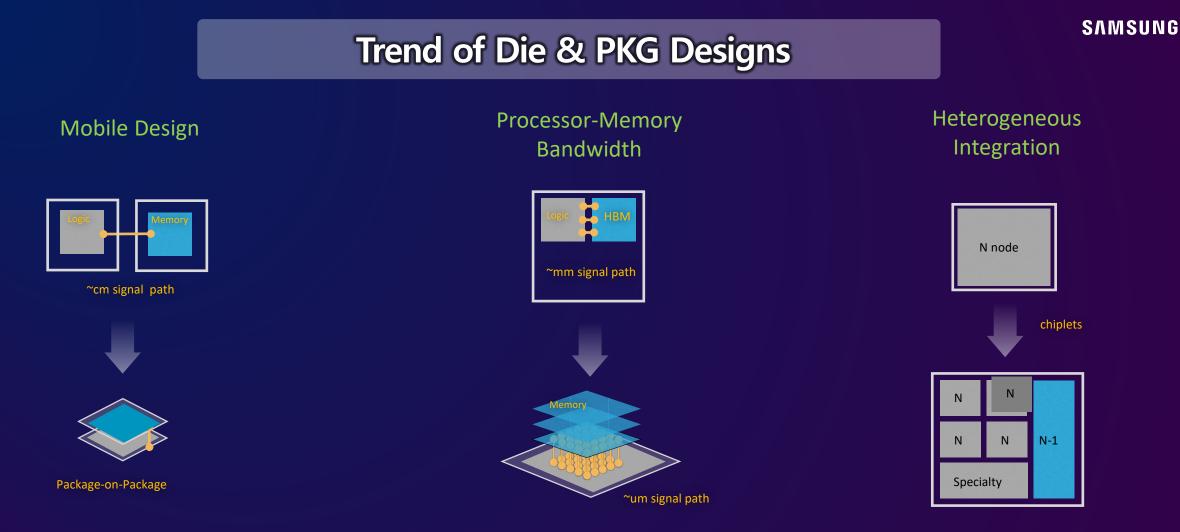

- Die/PKG designs are moving to 3D for performance and yield improvement

- Closer Proximity, Wider Bandwidth, Higher number of dies/chiplets

- The design granule for 3D is getting smaller

- Packaged-Device level  $\rightarrow$  die level  $\rightarrow$  block level (Chiplets)  $\rightarrow$  IP level

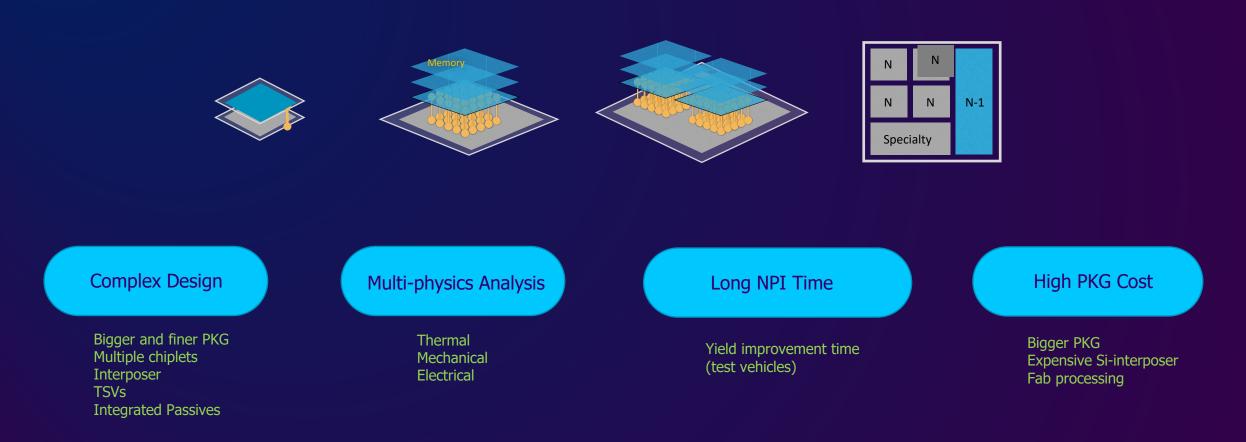

# Challenges for Wide-spread Use of 3D ICs & Adv. PKG

- 3D ICs will bring enormous innovations to the semiconductors

- However, we need solutions to overcome the challenges in 3D ICs

## Wishes for EDAs

- EDA tools that can make complex designs simpler

- Multi-physics analysis tools that can help reduce the analysis and yield improvement time

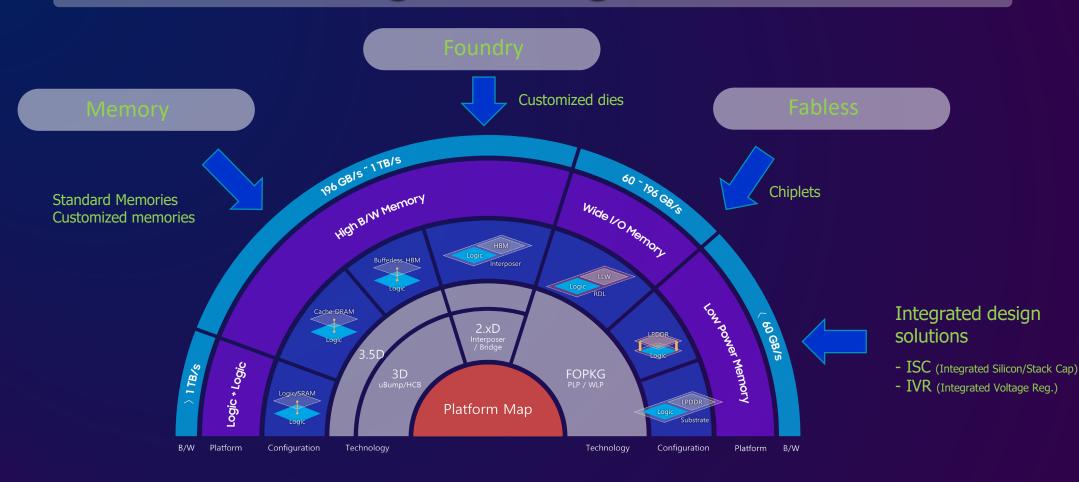

# Our Heterogeneous Integration Platforms

- Goals to achieve

- High performance

- Lower total cost

- Higher power efficiency

- Higher memory bandwidth

SAMSUNG

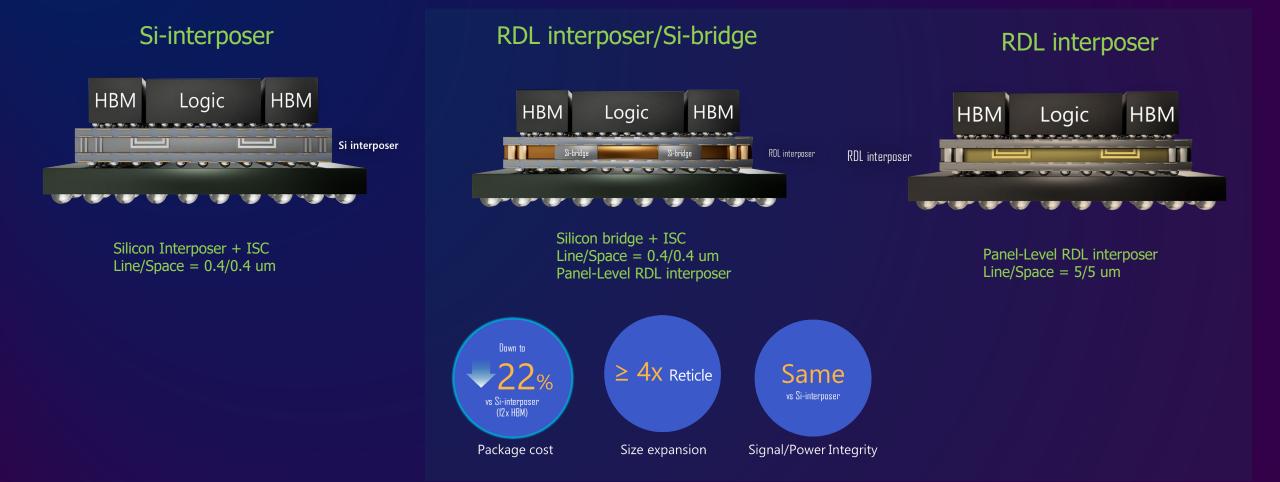

## **Cost-effective AI/HPC Package Platforms**

- Panel-level RDL interposer enables larger interposer, more HBMs and multi-dies for AI/Data-center applications

- Using Panel-level Packaging, we can lower the package cost and support bigger package size

## Summary

- Our answer to today's challenges is 3D ICs and Advanced Packaging

- Cost, Performance and Memory BW

- However, we need solutions to overcome the challenges for wide-spread use of 3D ICs

- Design is complex

- Analysis needs to consider multi-physics at the same time

- Long yield improvement time by using test vehicles

- High cost by using fab processing and expensive Si-interposer

- We are developing cost-effective and design-flexible packaging solutions for wide-spread use of 3D ICs that will boost the industry's innovation

- Finer-pitch uBump and Bump-less 3D stacking

- Panel-level based RDL interposer for AI/HPC applications

- Integrated design solutions